Product Summary

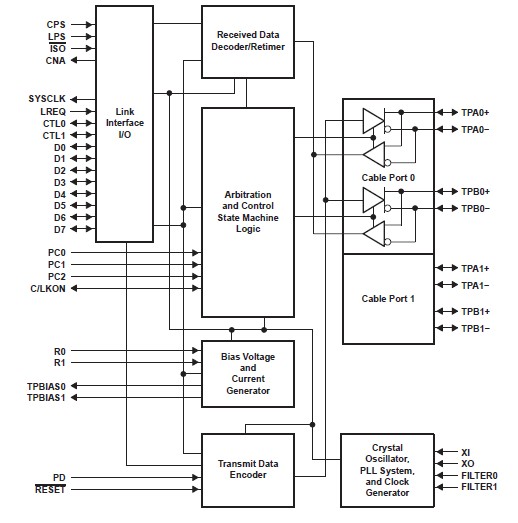

The TSB41AB2PAP is a two-port cable transcever/arbiter functions needed to implement a two-port node in a cable-based IEEE 1394 network. The cable ports incorporate two differential line transceivers. The transceivers include circuitry to monitor the line conditions as needed for determining connection status, for initialization and arbitration, and for packet reception and transmission. The TSB41AB2PAP is designed to interface with a link layer controller (LLC). The TSB41AB2PAP requires only an external 24.576-MHz crystal as a reference. An external clock may be provided instead of a crystal. An internal oscillator drives an internal phase-locked loop (PLL), which generates the required 393.216-MHz reference signal. This reference signal is internally divided to provide the clock signals used to control transmission of the outbound encoded strobe and data information. A 49.152-MHz clock signal is supplied to the associated LLC for synchronization of the two chips and is used for resynchronization of the received data. The power-down (PD) function, when enabled by asserting the PD terminal high, stops operation of the PLL.

Parametrics

TSB41AB2PAP absolute maximum ratings: (1)Supply voltage range, VDD: −0.3 V to 4 V; (2)Input voltage range, VI: −0.5 V to VDD + 0.5 V; (3)Output voltage range at any output, VO: −0.5 V to VDD + 0.5V; (4)Operating free air temperature, TA: 0°C to 70°C; (5)Storage temperature range, Tstg: −65°C to 150°C; (6)Lead temperature 1,6 mm (1/16 inch)from case for 10 seconds: 260°C.

Features

TSB41AB2PAP features: (1)fully interoperable with firewire and i.link implementation of ieee std 1394; (2)fully compliant with openhci requirements; (3)provides two ieee 1394a-2000 fully compliant cable ports at 100/200/400 megabits per second (mbits/s); (4)full ieee 1394a-2000 support includes: connection debounce, arbitrated short reset, multispeed concatenation, arbitration acceleration, fly-by concatenation, port disable/suspend/resume; (5)register bits give software control of contender bit, power class bits, link active control bit and ieee 1394a-2000 features; (6)ieee 1394a-2000 compliant common mode noise filter on incoming tpbias; (7)software device reset (swr); (8)industry leading low power consumption; (9)ultralow-power sleep mode; (10)cable power presence monitoring; (11)cable ports monitor line conditions for active connection to remote node; (12)data interface to link layer controller through 2/4/8 parallel lines at 49.152 mhz; (13)interface to link layer controller supports low-cost ti bus-holder isolation and optional annex j electrical isolation; (14)interoperable with link layer controllers using 3.3 v; (15)single 3.3-v supply operation; (16)low-cost 24.576-mhz crystal provides transmit, receive data at 100/200/400 mbits/s, and link-layer controller clock at 49.152 mhz.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

TSB41AB2PAP |

Texas Instruments |

Buffers & Line Drivers Two-Port Cable Xcvr/Arbiter |

Data Sheet |

|

|

||||||||||||

|

TSB41AB2PAPG4 |

Texas Instruments |

Buffers & Line Drivers Two-Port Cable Xcvr/Arbiter |

Data Sheet |

|

|

||||||||||||

|

TSB41AB2PAPRG4 |

Texas Instruments |

1394 Interface IC IEEE1394a 2Port Cable Xcvr/Arbiter |

Data Sheet |

|

|

||||||||||||

|

TSB41AB2PAPR |

Texas Instruments |

Buffers & Line Drivers Two-Port Cable Xcvr/Arbiter |

Data Sheet |

|

|

||||||||||||

(China (Mainland))

(China (Mainland))